#

#### **Copyright Notice**

Copyright© 1997-98 Chips and Technologies, Inc., a subsidiary of Intel Corporation. ALL RIGHTS RESERVED.

This manual is copyrighted by Chips and Technologies, Inc., a subsidiary of Intel Corporation. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language or computer language, in any form or by any means - electronic, mechanical, magnetic, optical, chemical, manual, or otherwise - any part of this publication without the express written permission of Chips and Technologies, Inc., a subsidiary of Intel Corporation.

#### **Restricted Rights Legend**

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at 252.277-7013.

#### **Trademark Acknowledgment**

CHIPS Logo is a registered trademark of Chips and Technologies, Inc., a subsidiary of Intel Corporation.

HiQVideo, is a trademark of Chips and Technologies, Inc., a subsidiary of Intel Corporation.

All other trademarks are the property of their respective holders.

#### Disclaimer

This document provides general information for the customer. Chips and Technologies, Inc., a subsidiary of Intel Corporation, reserves the right to modify the information contained herein as necessary and the customer should ensure that it has the most recent revision of the document. CHIPS makes no warranty for the use of its products and bears no responsibility for any errors which may appear in this document. The customer should be on notice that many different parties hold patents on products, components, and processes within the personal computer industry. Customers should ensure that their use of the products does not infringe upon any patents. CHIPS respects the patent rights of third parties and shall not participate in direct or indirect patent infringement.

# 69000 High Performance Flat Panel / CRT HiQVideo<sup>™</sup>Accelerator with Integrated Memory

- Highly integrated Flat Panel and CRT GUI Accelerator & Multimedia Engine, Palette/DAC, Clock Synthesizer, and integrated frame buffer

- Integrated High Performance SDRAM memory

- 2MB integrated memory

- 83 MHz SDRAM operation

- HiQColor<sup>™</sup> Technology implemented with

- TMED (Temporal Modulated Energy Distribution)

- Enables 16.7 Million colors on STN panel without *dither*

- Brighter and Crisper STN Image

- No shimmer or Mach bands on STN

- No crawling images on STN

- 256 gray shades per primary color

- Panel Tuning NOT required

- Hardware Windows Acceleration

- Single Cycle 64-bit Graphics Engine

- System-to-Screen and

- Screen-to-Screen BitBLT

- 3-Operand Raster-Ops

- 8/16/24 Color Expansion

- Transparent BLT

- Optimized for Windows<sup>TM</sup> BitBLT format

- Acceleration in ALL color modes

- Integrated composite NTSC / PAL Support

- Flicker Reduction Circuitry

- Hardware Multimedia Support

- Zoom Video port

- YUV input from System Bus or Video Port

- YUV-RGB Conversion

- · Capture / Scaling

- Video Zoom up to 8x

- Vertical interpolation of video data up to 720 pixels wide.

- Double Buffered Video

- Horizontal Interpolation

- Image Mirroring

- Display centering and stretching features for optimal fit of VGA graphics and text on 800x600 and 1024x768 panels

- Simultaneous Hardware Cursor and Pop-up Window

- 64x64 pixels by 4 colors

- 128x128 pixels by 2 colors

- PCI/Frame AGP Bus with Burst Mode capability and BIOS ROM support

- Power Sequencing control outputs regulate application of bias voltage, +5V to the panel and +12V to the inverter for backlight operation.

- 3.3V Operation, 5.0V tolerant I/O

- Game Acceleration

- Source Transparent BLT

- Destination Transparent BLT

- Double buffer support for YUV and 15/ 16Bpp Overlay Engine

- Instant Full Screen Page Flip

- Read back of CRT Scan line counters

- High-Performance Flat Panel Display resolutions and color depth at 3.3V

- 640x480 x 24bpp

- 800x600 x 24bpp

- 1024x768 x 16bpp

- 1280x1024 x 8bpp

- CRT Support

- Integrated high performance triple 8-bit, RAMDAC

- Flexible Panel Support

- Support for a wide variety of monochrome and color panels

- Single-Panel, Single-Drive (SS)

- Dual-Panel, Dual Drive (DD) passive STN

- Active matrix TFT/MIM LCD

- EL panels

- Plasma panels

- 36-bit direct interface to color and monochrome, single drive (SS), and dual drive (DD), STN & TFT panels

- Support for 16:9 aspect ratio panels

- Flexible On-chip Activity Timer facilitates ordered shut-down of the display system

- Advanced Power Management feature minimizes power usage in:

- Normal operation

- Standby (Sleep) modes

- Panel-Off Power-Saving Mode

- VESA Standards supported

- VAFC Port for display of "Live" Video

- DPMS for CRT power-down

- DDC for CRT Plug-Play & Display Control

- Fully Compatible with IBM<sup>®</sup> VGA

- Packages supported

- 272 PBGA

- 256 mBGA

# **69000 Software Support Features**

- Drivers Features

- High Performance Accelerated drivers

- Compatible across HiQVideo family

- Auto Panning Support

- LCD/CRT/Simultaneous Mode Support

- Auto Resolution Change

- HW Stretching/Scaling

- Double Buffering

- Internationalization

- ChipsCPL (Control Panel Applet)

- Direct Draw support

- Games SDK support

- Dynamic Resolution Switching

- VGA Graphics applications in Windows™

- VESA DDC extensions

- VESA DPMS extensions

- Property Sheet to change Refresh/ Display

- Seamless Windows Support

- Boot time resolution adjustment

- DIVE, EnDIVE

- DCAF

- Multimedia Software

- Video Port Manager for ZV Port

- PCVideo DLL plus Tuner with DK

Board

- Software Utilities

- DebugVGA

- Auto testing of all video modes

- ChipsVGA

- ChipsEXT

- Software Documentation

- BIOS OEM Reference Guide

- Display Driver User's Guide

- Utilities User's Guide

- Release Notes for BIOS, Drivers, and Utilities

- Software Support

- Dedicated Software Applications

Engineer

- BBS Support for Software Updates

- BIOS Features

- VGA Compatible BIOS

- PnP Support

- VESA VBE 2.0 (incl. DPMS)

- DDC 1, DDC 2AB

- Text and Graphics Expansion

- Auto Centering

- 44 (40) K BIOS

- CRT, LCD, Simultaneous display modes

- Auto Resolution Switch

- Multiple Refresh Rates

- NTSC/PAL support

- Extended Modes

- Extended BIOS Functions

- 1024x768 TFT, DSTN Color Panels

- Multiple Panel Support (8 panels builtin)

- Get Panel Type Function

- HW Popup Interface

- Monitor Detect

- Pop Up Support

- SMI and Hot Key support

- System BIOS Hooks

- Set Active Display Type

- Save/Restore Video State

- Setup Memory for Save/Restore

- SMI Entry Point

- Int 15 Calls after POST, Set Mode

- BIOS Modify Program (BMP)

- Clocks

- Mode support

- Panel Tables

- Int 15 Hooks

- Monitor Sensing

- Driver Support

- Windows 95

- Windows NT 4.0, NT 3.1

- Windows 98

- Win 31

# **Revision History**

| <u>Revision</u><br>0.1<br>0.2 | <b>Date</b><br>2/28/97<br>4/3/97 | <b>By</b><br>TE/lc/bjb<br>AS/bjb | <b>Comments</b><br>First Draft- Official Release<br>Change MCLK from 110MHz to 83MHz<br>Added HiQColor(features)<br>Updated Pin Descriptions<br>Updated Extension Registers<br>Update Multimedia Registers<br>Updated Electrical Specifications<br>Updated Appendix A                              |

|-------------------------------|----------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0                           | 8/18/97                          | AS/bjb                           | Remove NDA requirements and API status                                                                                                                                                                                                                                                             |

| 1.1                           | 10/10/97                         | BB/Inc                           | Reorganized chapters<br>Added Wide Extension Register chapter<br>Updated Flat Panel Registers<br>Updated CRT Controller Registers<br>Added Subsystem and Subvendor ID support                                                                                                                      |

| 1.2                           | 3/9/98                           | BB/Inc                           | Improved Status Register Descriptions<br>Improved Palette Register Chapter<br>Improved Extension Register Descriptions<br>Improved Flat Panel Register Descriptions<br>Improved Multimedia Register Descriptions<br>Improved BitBLT Engine Register Descriptions<br>Updated Specifications chapter |

| 1.3                           | 7/1/98                           | BB/bjb                           | Added bullet-item for Frame-Based AGP Support<br>Added mBGA package pinout and pin numbering<br>Added Frame-Based AGP Interface timings<br>Added mBGA package mechanical specifications<br>Add differences between PCI-66/Frame-Based AGP                                                          |

| List Of Figures | xv   |

|-----------------|------|

| List of Tables  | xvii |

### Chapter 1

#### Introduction / Overview

| High Performance Integrated Memory        | 1-1 |

|-------------------------------------------|-----|

| Frame-Based AGP Compatibility             | 1-1 |

| HiQColor™ Technology                      | 1-1 |

| Versatile Panel Support                   | 1-1 |

| Acceleration for All Panels and All Modes | 1-1 |

| Television NTSC/PAL Flicker Free Output   | 1-1 |

| HiQVideo™ Multimedia Support              | 1-3 |

| Low Power Consumption                     | 1-3 |

| Software Compatibility/Flexibility        |     |

| Display Modes Supported                   |     |

|                                           |     |

### Chapter 2

### Pin Descriptions

| Pin Diagram, Top View, Ball Grid Array         | 2-1  |

|------------------------------------------------|------|

| Pin Diagram, Bottom View, Ball Grid Array      | 2-2  |

| Pin Diagram, Top View, Mini Ball Grid Array    | 2-3  |

| Pin Diagram, Bottom View, Mini Ball Grid Array | 2-4  |

| PCI/AGP Bus Interface                          | 2-5  |

| Configuration Pins and ROM Interface           |      |

| Flat Panel Display Interface                   |      |

| CRT Interface                                  | 2-12 |

| Video Interface                                | 2-13 |

| Miscellaneous                                  | 2-14 |

| Power and Ground                               | 2-15 |

| Reserved and No Connect                        | 2-17 |

|                                                |      |

# Chapter 3 Electrical Specifications

| Absolute Maximum Conditions                                | 3-1 |

|------------------------------------------------------------|-----|

| Normal Operating Conditions                                | 3-1 |

| DAC Characteristics                                        |     |

| DC Characteristics                                         |     |

| DC Drive Characteristics                                   | 3-2 |

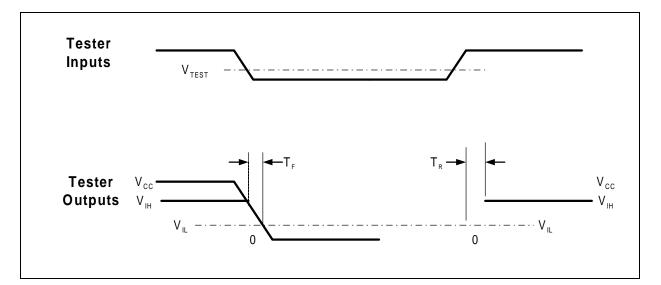

| AC Test Conditions                                         | 3-3 |

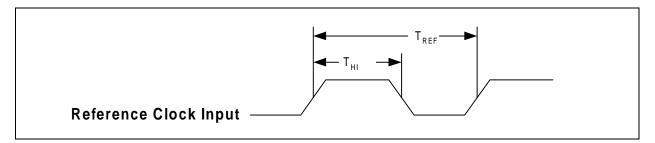

| AC Timing Characteristics - Reference Clock                | 3-4 |

| AC Timing Characteristics - Clock Generator                |     |

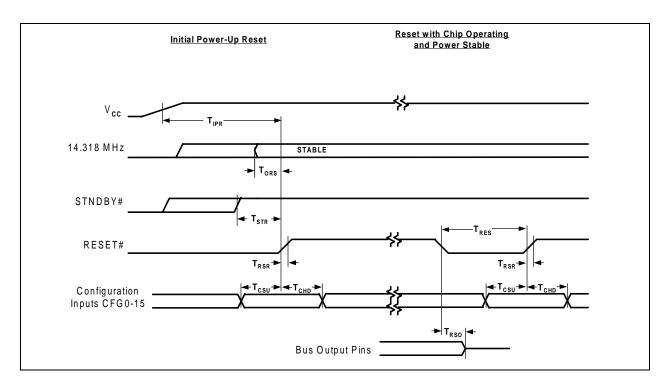

| AC Timing Characteristics - Reset                          |     |

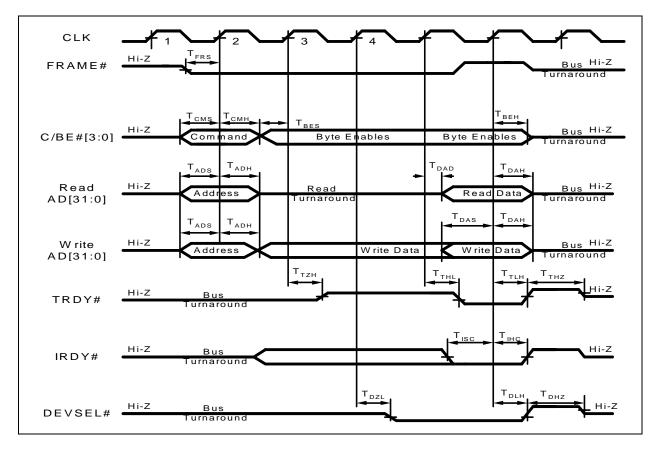

| AC Timing Characteristics - PCI Bus Frame (CLK = 33MHz)    |     |

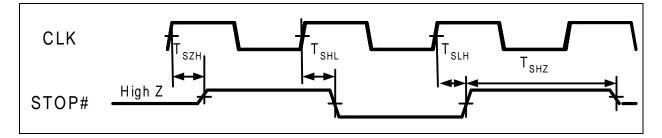

| AC Timing Characteristics - PCI Bus Stop (CLK = 33MHz).    |     |

| AC Timing Characteristics - BIOS ROM                       |     |

| AC Timing Characteristics - Video Data Port                |     |

| AC Timing Characteristics - Panel Output Timing            |     |

| AC Timing Characteristics - A.G.P. 1x AC Timing Parameters |     |

| 5                                                          |     |

#### Chapter 4

| Mechanical Specifications4-2 |

|------------------------------|

|------------------------------|

V

#### Chapter 5 I/O and Memory Address Maps

| I/O and Memory Address Map            | . 5-1 |

|---------------------------------------|-------|

| VGA-Compatible Address Map            |       |

| Address Maps for Going Beyond VGA     |       |

| PCI Configurations Registers          |       |

| I/O and Sub-Addressed Register Map    |       |

| Sub-Addressing Indexes and Data Ports |       |

| Lower Memory Map                      |       |

| Upper Memory Map                      |       |

|                                       | -     |

#### Chapter 6 Register Summaries

| _ |                                        |       |

|---|----------------------------------------|-------|

|   | PCI Configuration Registers            | . 6-1 |

|   | General Control & Status Registers     | . 6-1 |

|   | CRT Controller Registers               | . 6-2 |

|   | Sequencer Registers                    | . 6-3 |

|   | Graphics Controller Registers          | . 6-3 |

|   | Attribute Controller Registers         | . 6-3 |

|   | Palette Registers                      | . 6-3 |

|   | Extension Registers                    |       |

|   | Flat Panel Registers                   | . 6-6 |

|   | Multimedia Registers                   | . 6-7 |

|   | BitBLT Registers                       |       |

|   | Memory Mapped Wide Extension Registers |       |

|   |                                        |       |

### Chapter 7

### PCI Configuration Registers

| VENDID Vendor ID Register                             | 7-2  |

|-------------------------------------------------------|------|

| VENDID Vendor ID Register<br>DEVID Device ID Register | 7-2  |

| DEVCTL Device Control Register                        |      |

| DEVSTAT Device Status Register                        | 7-5  |

| REV Revision ID Register                              |      |

| PRG Register-Level Programming Interface Register     | 7-7  |

| SUB Sub-Class Code Register                           | 7-8  |

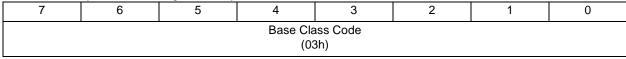

| BASE Base Class Code Register                         |      |

| HDR Header Type Register                              | 7-9  |

| MBASE Memory Base Address Register                    | 7-10 |

| SUBVENDID Subsystem Vendor ID Register                | 7-11 |

| SUBDEVDID Subsystem Device ID Register                |      |

| INTLINE Interrupt Line Register                       | 7-12 |

| INTPIN Interrupt Pin Register                         | 7-12 |

| RBASE ROM Base Address Register                       | 7-13 |

| SUBVENDSET Subsystem Vendor ID Set Register           | 7-14 |

| SUBDEVSET Subsystem Device ID Set Register            | 7-14 |

|                                                       |      |

#### Chapter 8

### General Control and Status Registers

| ST00 Input Status Register 0      | 8-2 |

|-----------------------------------|-----|

| ST01 Input Status Register 1      |     |

| FCR Feature Control Register      |     |

| MSR Miscellaneous Output Register |     |

|                                   |     |

# Chapter 9 CRT Controller Registers

| CRX  | CRT Controller Index Register                   | 9-2   |

|------|-------------------------------------------------|-------|

| CR00 | Horizontal Total Register                       | 9-3   |

| CR01 | Horizontal Display Enable End Register          | 9-3   |

| CR02 | Horizontal Blanking Start Register              | 9-3   |

| CR03 | Horizontal Blanking End Register                | 9-4   |

| CR04 | Horizontal Sync Start Register                  | 9-5   |

| CR05 | Horizontal Sync End Register                    | 9-6   |

| CR06 | Vertical Total Register                         | 9-7   |

| CR07 | Overflow Register                               | 9-8   |

| CR08 | Preset Row Scan Register                        | .9-12 |

| CR09 | Maximum Scanline Register                       | .9-13 |

| CR0A | Text Cursor Start Register                      | .9-15 |

| CR0B | Text Cursor End Register                        | .9-16 |

| CR0C | Start Address High Register                     | .9-17 |

| CR0D | Start Address Low Register                      |       |

| CR0E | Text Cursor Location High Register              |       |

| CR0F | Text Cursor Location Low Register               |       |

| CR10 | Vertical Sync Start Register                    |       |

| CR11 | Vertical Sync End Register                      |       |

| CR12 | Vertical Display Enable End Register            |       |

| CR13 | Offset Register                                 |       |

| CR14 | Underline Location Register                     |       |

| CR15 | Vertical Blanking Start Register                |       |

| CR16 | Vertical Blanking End Register                  |       |

| CR17 | CRT Mode Control                                |       |

| CR18 | Line Compare Register                           |       |

| CR22 | Memory Read Latch Data Register                 |       |

| CR30 | Extended Vertical Total Register                |       |

| CR31 | Extended Vertical Display End Register          |       |

| CR32 | Extended Vertical Sync Start Register           |       |

| CR33 | Extended Vertical Blanking Start Register       |       |

| CR38 | Extended Horizontal Total Register              |       |

| CR3C | Extended Horizontal Blanking End Register       |       |

| CR40 | Extended Start Address Register                 | .9-34 |

| CR41 | Extended Offset Register                        |       |

| CR70 | Interlace Control Register                      |       |

| CR71 | NTSC/PAL Video Output Control Register          |       |

| CR72 | NTSC/PAL Horizontal Serration 1 Start Register  |       |

| CR73 | NTSC/PAL Horizontal Serration 2 Start Register  |       |

| CR74 | NTSC/PAL Horizontal Pulse Width Register        |       |

| CR75 | NTSC/PAL Filtering Burst Read Length Register   |       |

| CR76 | NTSC/PAL Filtering Burst Read Quantity Register |       |

| CR77 | NTSC/PAL Filtering Control Register             |       |

| CR78 | NTSC/PAL Vertical Reduction Register            |       |

| CR79 | NTSC/PAL Horizontal Total Fine Adjust Register  |       |

|      | , ,                                             |       |

#### Chapter 10 Sequencer Registers

|      | (egisters                                   |  |

|------|---------------------------------------------|--|

| SRX  | Sequencer Index Register                    |  |

| SR00 | Reset Register                              |  |

| SR01 | Clocking Mode Register                      |  |

| SR02 | Plane Mask Register                         |  |

| SR03 | Character Map Select Register               |  |

| SR04 | Memory Mode Register                        |  |

| SR07 | Horizontal Character Counter Reset Register |  |

|      |                                             |  |

#### Chapter 11

#### Graphics Controller Registers

|      | 5                                 |       |

|------|-----------------------------------|-------|

| GRX  | Graphics Controller Index Registe | r11-2 |

| GR00 | Set/Reset Register                |       |

| GR01 | Enable Set/Reset Register         |       |

| GR02 | Color Compare Register            |       |

| GR03 | Data Rotate Register              |       |

| GR04 | Read Plane Select Register        |       |

| GR05 | Graphics Mode Register            |       |

| GR06 | Miscellaneous Register            |       |

| GR07 | Color Don't Care Register         |       |

| GR08 | Bit Mask Register                 |       |

|      |                                   |       |

#### Chapter 12

#### Attribute Controller Registers

| 12-2 |

|------|

| 12-2 |

| 12-3 |

| 12-4 |

| 12-5 |

| 12-6 |

| 12-7 |

|      |

#### Chapter 13

#### Palette Registers

| PALMASK  | Palette Data Mask Register   | .13-3  |

|----------|------------------------------|--------|

| PALSTATE | Palette State Register       | .13-3  |

|          | Palette Read Index Register  |        |

| PALWX    | Palette Write Index Register | . 13-4 |

| PALDATA  | Palette Data Register        | .13-5  |

#### Chapter 14

#### **Extension Registers**

| XRX  | Extension Register Index Register | 14-3 |

|------|-----------------------------------|------|

| XR00 | Vendor ID Low Register            |      |

| XR01 | Vendor ID High Register           |      |

| XR02 | Device ID Low Register            |      |

| XR03 | Device ID High Register           |      |

| XR04 | Revision ID Register              |      |

| XR05 | Linear Base Address Low Register  |      |

| XR06 | Linear Base Address High Register |      |

| XR08 | Host Bus Configuration Register   |      |

|      |                                   |      |

| XR09 | I/O Control Register              | 14-8 |

|      |                                   |      |

| XR0A   | Frame Buffer Mapping Register           | 14-9  |

|--------|-----------------------------------------|-------|

| XR0B   | PCI Burst Write Support Register        |       |

| XR0E   | Frame Buffer Page Select Register       | 14-12 |

| XR20   | BitBLT Configuration Register           |       |

| XR40   | Memory Access Control Register          |       |

| XR41-X |                                         |       |

| XR60   | Video Pin Control Register              |       |

| XR61   | DPMS Sync Control Register              | 14-16 |

| XR62   | GPIO Pin Control Register               | 14-17 |

| XR63   | GPIO Pin Data Register                  | 14-18 |

| XR67   | Pin Tri-State Control Register          | 14-19 |

| XR70   | Configuration Pins 0 Register           | 14-20 |

| XR71   | Configuration Pins 1 Register           | 14-22 |

| XR80   | Pixel Pipeline Configuration 0 Register | 14-23 |

| XR81   | Pixel Pipeline Configuration 1 Register | 14-25 |

| XR82   | Pixel Pipeline Configuration 2 Register | 14-26 |

| XRA0   | Cursor 1 Control Register               | 14-27 |

| XRA1   | Cursor 1 Vertical Extension Register    | 14-28 |

| XRA2   | Cursor 1 Base Address Low Register      | 14-28 |

| XRA3   | Cursor 1 Base Address High Register     | 14-29 |

| XRA4   | Cursor 1 X-Position Low Register        | 14-29 |

| XRA5   | Cursor 1 X-Position High Register       | 14-30 |

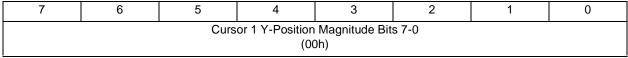

| XRA6   | Cursor 1 Y-Position Low Register        | 14-30 |

| XRA7   | Cursor 1 Y-Position High Register       | 14-31 |

| XRA8   | Cursor 2 Control Register               | 14-32 |

| XRA9   | Cursor 2 Vertical Extension Register    |       |

| XRAA   | Cursor 2 Base Address Low Register      |       |

| XRAB   | Cursor 2 Base Address High Register     |       |

| XRAC   | Cursor 2 X-Position Low Register        |       |

| XRAD   | Cursor 2 X-Position High Register       |       |

| XRAE   | Cursor 2 Y-Position Low Register        |       |

| XRAF   | Cursor 2 Y-Position High Register       |       |

| XRC0   | Dot Clock 0 VCO M-Divisor Register      |       |

| XRC1   | Dot Clock 0 VCO N-Divisor Register      |       |

| XRC3   | Dot Clock 0 Divisor Select Register     |       |

| XRC4   | Dot Clock 1 VCO M-Divisor Register      |       |

| XRC5   | Dot Clock 1 VCO N-Divisor Register      |       |

| XRC7   | Dot Clock 1 Divisor Select Register     |       |

| XRC8   | Dot Clock 2 VCO M-Divisor Register      |       |

| XRC9   | Dot Clock 2 VCO N-Divisor Register      |       |

| XRCB   | Dot Clock 2 Divisor Select Register     |       |

| XRCC   | Memory Clock VCO M-Divisor Register     |       |

| XRCD   | Memory Clock VCO N-Divisor Register     |       |

| XRCE   | Memory Clock Divisor Select Register    |       |

| XRCF   | Clock Configuration Register            |       |

| XRD0   | Powerdown Control Register              |       |

| XRD1   | Power Conservation Control Register     |       |

| XRD2   | 2KHz Down Counter Register              |       |

| XRE0-> | 5 5                                     |       |

| XRF8-> | (RFC Test Registers                     | 14-48 |

# Chapter 15 Flat Panel Registers

| FR00 | Feature Register          | 15-2 |

|------|---------------------------|------|

| FR01 | CRT / FP Control Register | 15-2 |

| FR03   | FP Dot Clock Source Register                   |       |

|--------|------------------------------------------------|-------|

| FR04   | Panel Power Sequencing Delay Register          |       |

| FR05   | Power Down Control 1 Register                  |       |

| FR06   | FP Power Down Control Register                 |       |

| FR08   | FP Pin Polarity Register                       | 15-7  |

| FR0A   | Programmable Output Drive Register             | 15-8  |

| FR0B   | FP Pin Control 1 Register                      |       |

| FR0C   | Pin Control 2 Register                         | 15-10 |

| FR0F   | Activity Timer Control Register                | 15-11 |

| FR10   | FP Format 0 Register                           | 15-12 |

| FR11   | FP Format 1 Register                           | 15-14 |

| FR12   | FP Format 2 Register                           | 15-16 |

| FR13   | FP Format 3 Register                           | 15-18 |

| FR16   | FRC Option Select Register                     | 15-19 |

| FR17   | Polynomial FRC Control Register                | 15-20 |

| FR18   | FP Text Mode Control Register                  | 15-20 |

| FR19   | Blink Rate Control Register                    | 15-21 |

| FR1A   | STN-DD Buffering Control Register              | 15-22 |

| FR1E   | M (ACDCLK) Control Register                    | 15-22 |

| FR1F   | Diagnostic Register                            | 15-23 |

| FR20   | FP Horizontal Panel Display Size LSB Register  | 15-24 |

| FR21   | FP Horizontal Sync Start LSB Register          | 15-24 |

| FR22   | FP Horizontal Sync End Register                | 15-25 |

| FR23   | FP Horizontal Total LSB Register               | 15-25 |

| FR24   | FP HSync (LP) Delay LSB Register               | 15-26 |

| FR25   | FP Horizontal Overflow 1 Register              |       |

| FR26   | FP Horizontal Overflow 2 Register              | 15-27 |

| FR27   | FP HSync (LP) Width and Disable Register       | 15-27 |

| FR30   | FP Vertical Panel Size LSB Register            |       |

| FR31   | FP Vertical Sync Start LSB (FR31) Register     | 15-28 |

| FR32   | FP Vertical Sync End Register                  | 15-29 |

| FR33   | FP Vertical Total Register                     | 15-29 |

| FR34   | FP VSync (FLM) Delay Register                  | 15-30 |

| FR35   | FP Vertical Overflow 1 Register                |       |

| FR36   | FP Vertical Overflow 2 Register                | 15-31 |

| FR37   | FP VSync (FLM) Disable                         |       |

| FR40   | Horizontal Compensation Register               | 15-32 |

| FR41   | Horizontal Stretching Register                 |       |

| FR48   | Vertical Compensation Register                 |       |

| FR49-4 | 0 0                                            |       |

| FR4D   | Vertical Line Replication Register             |       |

| FR4E   | Selective Vertical Stretching Disable Register |       |

| FR70   | TMED Red Seed Register                         |       |

| FR71   | TMED Green Seed Register                       |       |

| FR72   | TMED Blue Seed Register                        |       |

| FR73   | TMED Control Register                          |       |

| FR74   | TMED2 Control Register                         | 15-40 |

# Chapter 16 Multimedia Registers

| MR00 | Module Capability Register    | 16-2   |

|------|-------------------------------|--------|

|      | Secondary Capability Register |        |

| MR02 | Capture Control 1 Register    | .16-3  |

| MR03 | Capture Control 2 Register    | .16-4  |

| MR04 | Capture Control 3 Register    | . 16-5 |

#### Chapter 17

#### **BitBLT Registers**

| BR00 | Source and Destination Span Register                                  | 17-2    |

|------|-----------------------------------------------------------------------|---------|

| BR01 | Pattern/Source Expansion Background Color & Transparency Key Register | 17-3    |

| BR02 | Pattern/Source Expansion Foreground Color Register                    | 17-4    |

| BR03 | Monochrome Source Control Register                                    | 17-5    |

| BR04 | BitBLT Control Register                                               | 17-7    |

| BR05 | Pattern Address Register                                              | . 17-11 |

| BR06 | Source Address Register                                               | 17-12   |

| BR07               | Destination Address Register                                  | 17-13 |

|--------------------|---------------------------------------------------------------|-------|

| BR08               | Destination Width & Height Register                           |       |

| BR09               | Source Expansion Background Color & Transparency Key Register |       |

| BR0A               | Source Expansion Foreground Color Register                    | 17-16 |

| Chapter 18         |                                                               |       |

| •                  | oped Wide Extension Registers                                 |       |

| ER00               | Central Interrupt Control Register                            |       |

| ER01               | Central Interrupt Status/Acknowledge Register                 |       |

| ER03               | Miscellaneous Function Register                               |       |

| Appendix A         |                                                               |       |

| <b>Display Mod</b> | es                                                            | A-1   |

| CRT-O              | nly Display Modes                                             | A-2   |

| Standa             | d VGA CRT-Only Display Modes                                  | A-2   |

| Chips E            | xtended VGA CRT-Only Display Modes                            | A-3   |

| Display            | Modes                                                         | A-6   |

|                    | nel-Only and Simultaneous 640x480 (VGA) Display Modes         |       |

| Flat Pa            | nel-Only and Simultaneous 800x600 (SVGA) Display Modes        | A-7   |

| Flat Pa            | nel-Only and Simultaneous 1024x768 Display Modes              | A-8   |

| Flat Pa            | nel-Only and Simultaneous 1280x1024 Display Modes             | A-9   |

|                    |                                                               |       |

### Appendix B

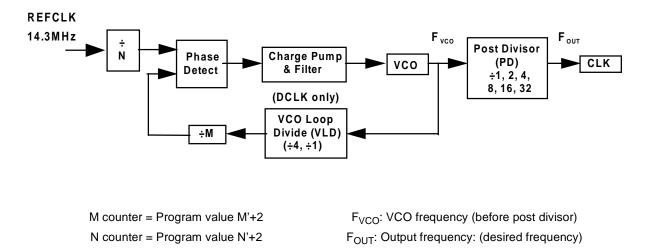

| Clock Generation                  | B-1 |

|-----------------------------------|-----|

| Clock Synthesizer                 | B-1 |

| Dot Clock (DCLK)                  | B-1 |

| Memory Clock (MCLK)               |     |

| PLL Parameters                    |     |

| Programming the Clock Synthesizer | B-3 |

| DCLK Programming                  |     |

| MCLK Programming                  | B-3 |

| Programming Constraints           | B-4 |

| Programming Example               | B-4 |

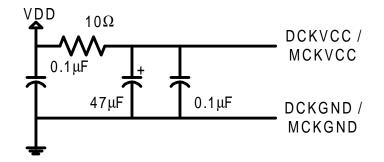

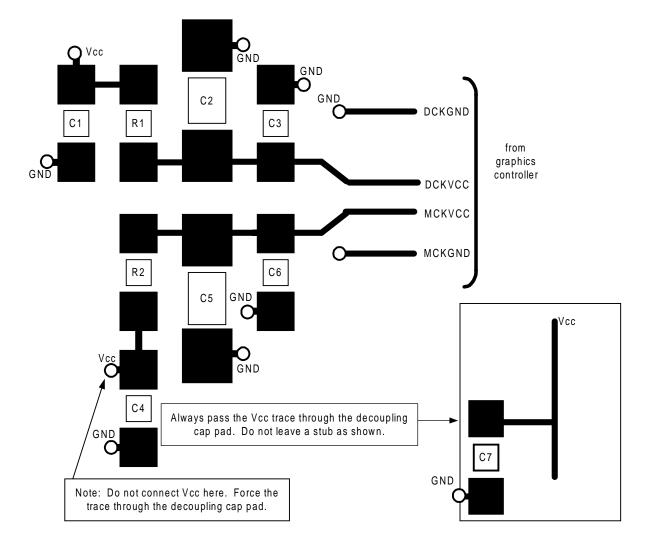

| PCB Layout Considerations         | B-5 |

| Display Memory Bandwidth          | B-7 |

| STN-DD Panel Buffering            |     |

| Horizontal and Vertical Clocking  |     |

| •                                 |     |

### Appendix C

| nel Power SequencingC-1 |

|-------------------------|

|-------------------------|

### Appendix D

| Hardware Cursor and Pop Up Window                 | D-1 |

|---------------------------------------------------|-----|

| Basic Cursor Configuration                        | D-1 |

| Base Address for Cursor Data                      | D-2 |

| Cursor Vertical Extension                         | D-2 |

| Cursor Colors                                     | D-2 |

| Cursor Positioning                                | D-3 |

| Cursor Modes                                      | D-3 |

| 32x32x2bpp & 64x64x2bpp AND/XOR Pixel Plane Modes | D-4 |

| 64x64x2bpp 4-Color Mode                           | D-6 |

| 64x64x2bpp 3-Color and Transparency Mode          | D-7 |

| 128x128x1bpp 2-Color Mode                         | D-8 |

| 128x128x1bpp 1-Color and Transparency Mode        | D-9 |

### Appendix E BitBLT Oper

| BitBLT Operation                                              |      |

|---------------------------------------------------------------|------|

| Introduction                                                  | E-1  |

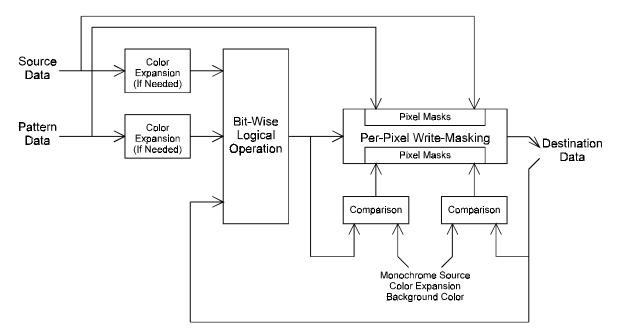

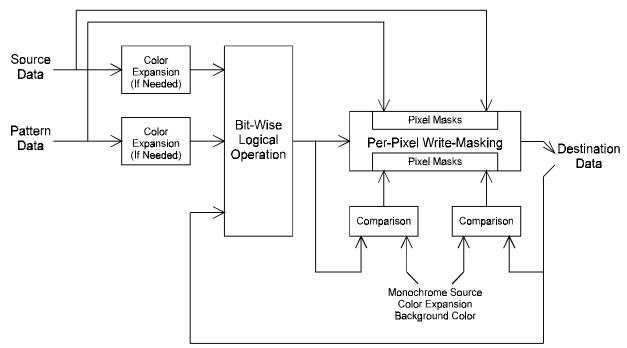

| Color Depth Configuration and Color Expansion                 | E-2  |

| Graphics Data Size Limitations                                | E-3  |

| Bit-Wise Operations                                           | E-3  |

| Per-Pixel Write-Masking Operations                            | E-7  |

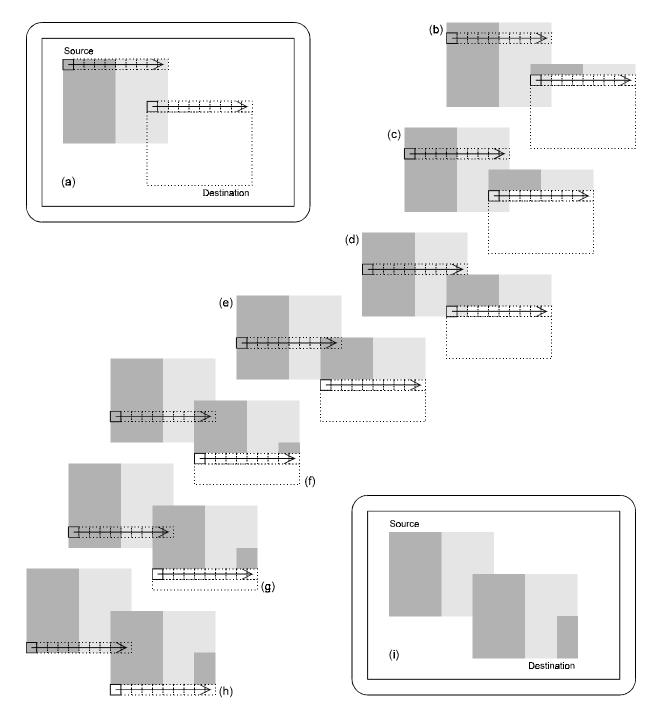

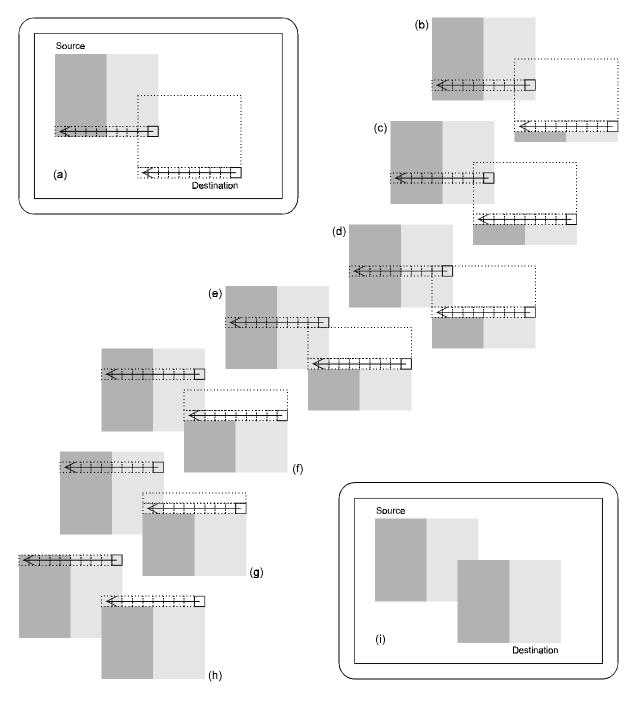

| When the Source and Destination Locations Overlap             | E-8  |

| Contiguous vs. Discontiguous Graphics Data                    |      |

| Source Data                                                   | E-13 |

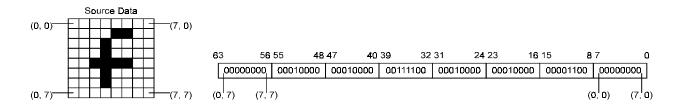

| Monochrome Source Data                                        | E-14 |

| Pattern Data                                                  |      |

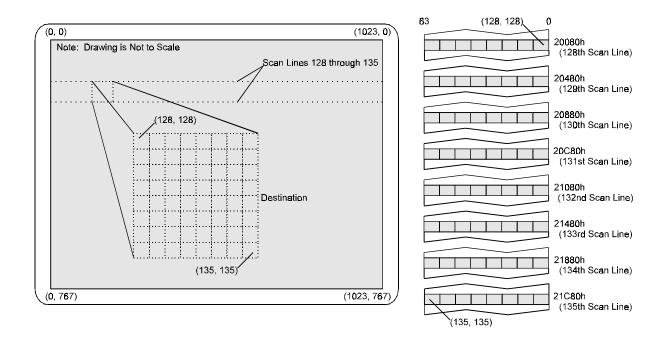

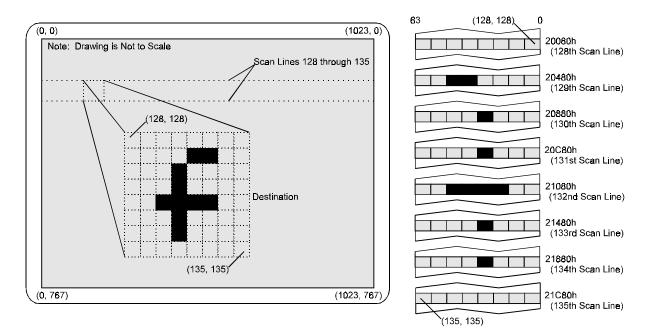

| Destination Data                                              | E-17 |

| BitBLT Programming Examples Pattern Fill A Very Simple BitBLT | E-18 |

| Drawing Characters Using a Font Stored in System Memory       |      |

# **List Of Figures**

| Figure 1-1: | Pixel Averaging Circuit                                                 | 1-2  |

|-------------|-------------------------------------------------------------------------|------|

| Figure 1-3: | Data Pipeline After MMUX, 2 Clocking                                    | 1-4  |

| •           | Pin Diagram, Top View, Ball Grid Array                                  |      |

|             | Pin Diagram, Bottom View, Ball Grid Array                               |      |

|             | Pin Diagram, Top View, Mini Ball Grid Array                             |      |

| Figure 2-4: | Pin Diagram, Bottom View, Mini Ball Grid Array                          | 2-4  |

|             | AC Test Timing                                                          |      |

| Figure 3-2: | Reference Clock Timing                                                  | 3-4  |

| Figure 3-3: | Reset Timing                                                            | 3-5  |

| Figure 3-4: | PCI Bus Frame Timing                                                    | 3-6  |

| Figure 3-5: | PCI Bus Stop Timing                                                     | 3-7  |

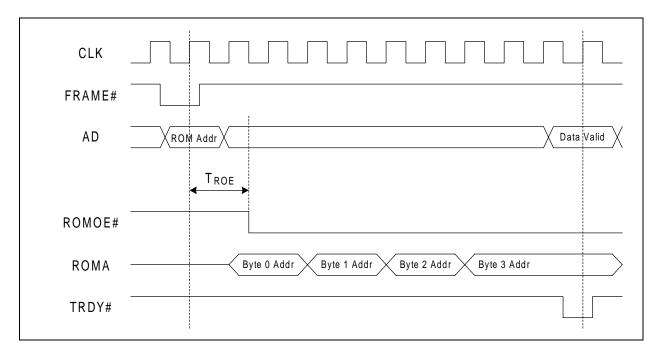

| Figure 3-6: | BIOS ROM Timing                                                         | 3-8  |

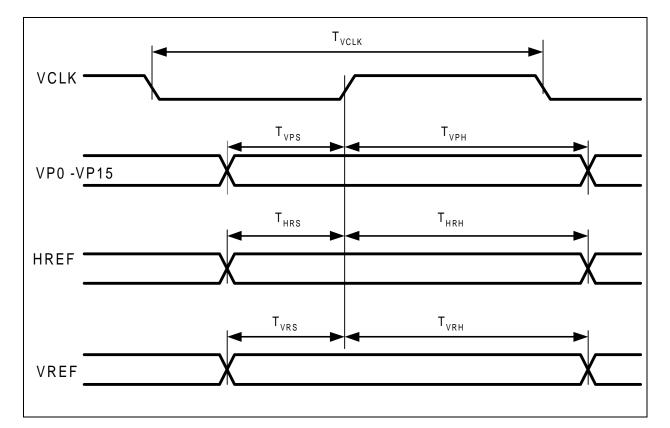

| Figure 3-7: | Video Data Port Timing                                                  | 3-9  |

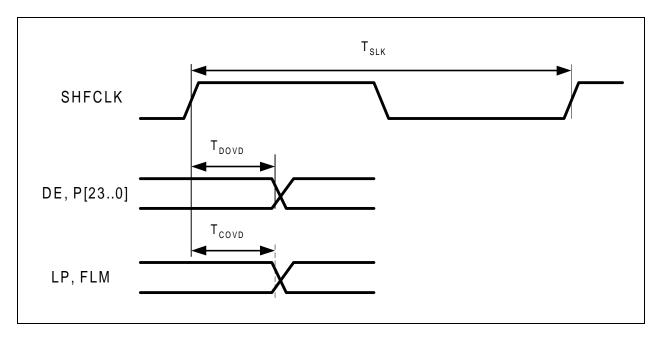

| Figure 3-8: | Panel Output Timing                                                     | 3-10 |

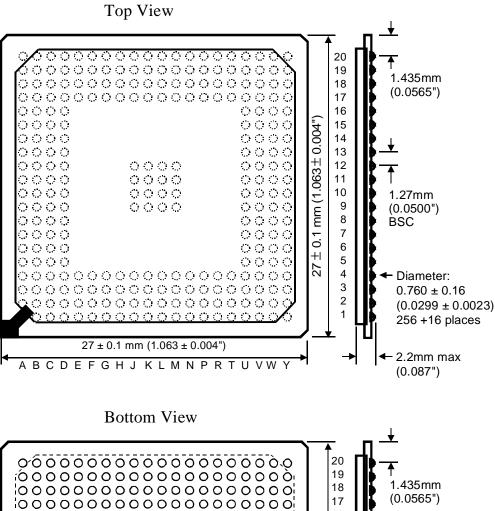

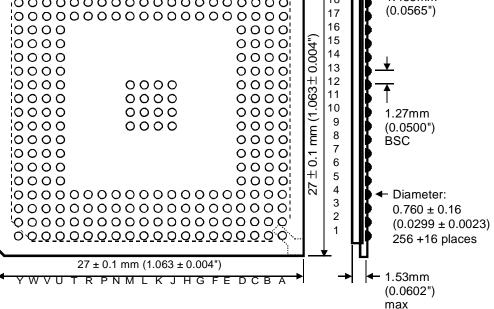

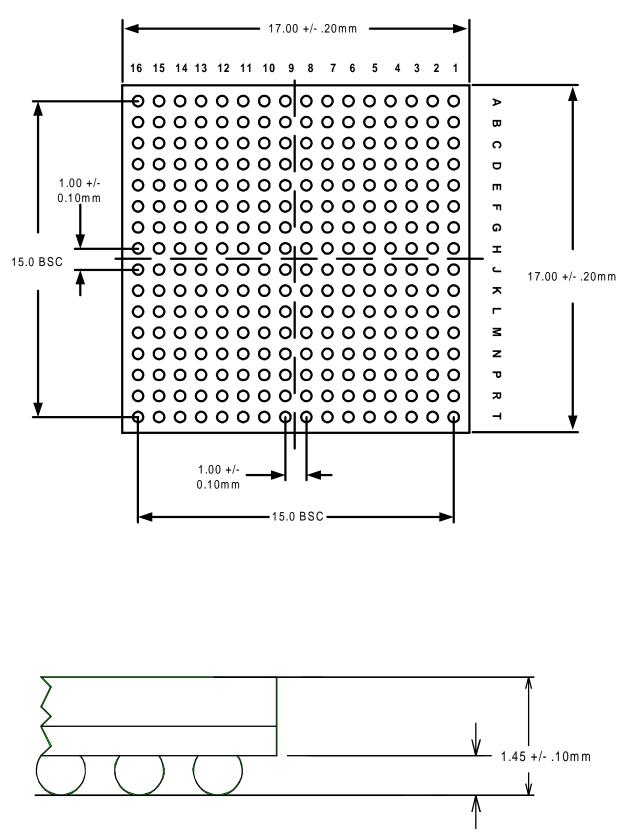

| Figure 4-1: | 256+16 - Contact Ball Grid Array                                        | 4-1  |

| Figure 4-2: | 256 Ball - mini Ball Grid Array                                         | 4-2  |

| Figure B-1: | PLL Elements                                                            | B-2  |

| Figure E-1: | Block Diagram and Data Paths of the BitBLT Engine                       | E-1  |

| Figure E-2: | Block Diagram and Data Paths of the BitBLT Engine                       | E-7  |

| Figure E-3: | Source Corruption in BitBLT with Overlapping Source and Destination     | E-8  |

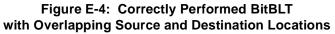

| Figure E-4: | Correctly Performed BitBLT with Overlapping Source and Destination      | E-10 |

|             | Suggested Starting Points for Source and Destination Overlap Situations |      |

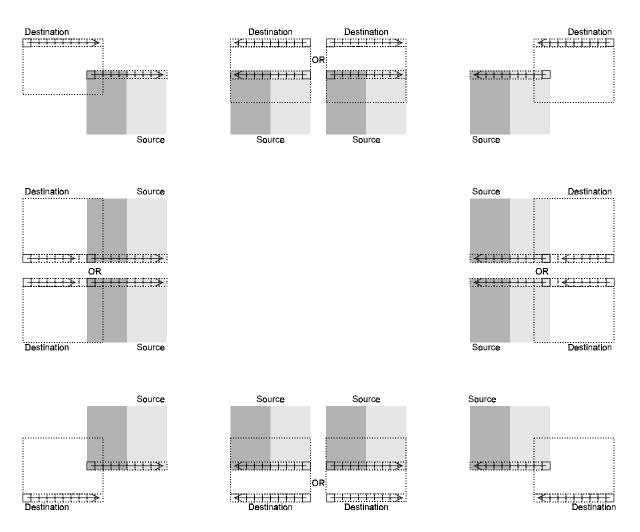

| Figure E-6: | On-Screen Single 6-Pixel Line in the Frame Buffer                       | E-12 |

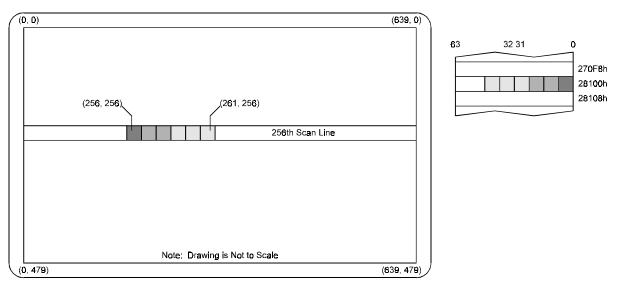

| Figure E-7: | On-Screen 6x4 Array of Pixels in the Frame Buffer                       | E-13 |

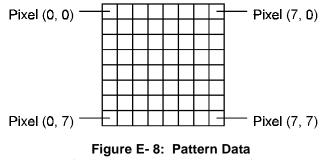

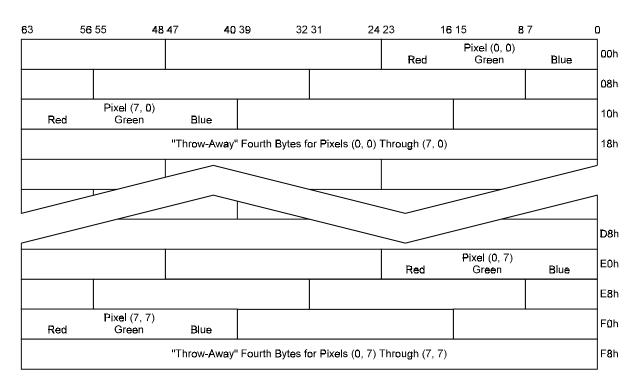

|             | Pattern Data                                                            |      |

|             | Monochrome Pattern Data Occupies a Single Quadword                      |      |

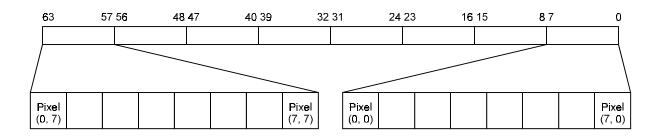

|             | : 8bpp Pattern Data Occupies 64 Bytes (8 Quadwords)                     |      |

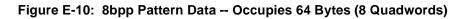

|             | : 16bpp Pattern Data Occupies 128 Bytes (16 Quadwords)                  |      |

|             | 2: 24bpp Pattern Data Occupies 256 Bytes (32 Quadwords)                 |      |

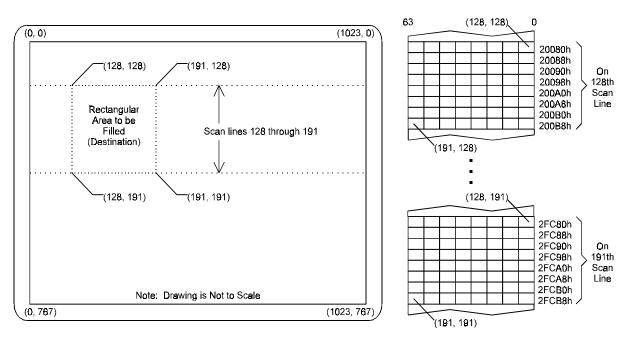

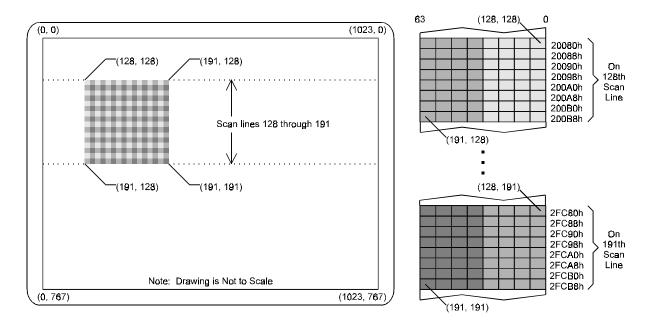

|             | : On-Screen Destination for Example Pattern Fill BitBLT                 |      |

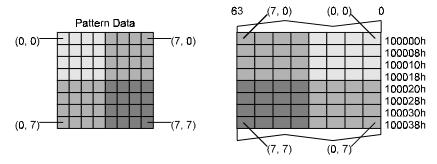

|             | : Pattern Data for Example Pattern Fill BitBLT                          |      |

|             | : Results of Example Pattern Fill BitBLT                                |      |

|             | : On-Screen Destination for Example Character Drawing BitBLT            |      |

|             | 7: Source Data in System Memory for Example Character Drawing BitBLT    |      |

| Figure E-18 | : Results of Example Character Drawing BitBLT                           | E-23 |

# **List of Tables**

| Table 1-1: 69000 Mode Support                                                      |     |

|------------------------------------------------------------------------------------|-----|

| Table 3-1: Absolute Maximum Conditions                                             |     |

| Table 3-2: Normal Operating Conditions                                             |     |

| Table 3-3: DAC Characteristics                                                     |     |

| Table 3-4: DC Characteristics                                                      |     |

| Table 3-5: DC Drive Characteristics                                                |     |

| Table 3-6: AC Test Conditions                                                      |     |

| Table 3-7: AC Timing Characteristics - Reference Clock                             |     |

| Table 3-8: AC Timing Characteristics - Clock Generator                             |     |

| Table 3-9: AC Timing Characteristics - Reset                                       |     |

| Table 3-10: AC Timing Characteristics - PCI Bus Frame (CLK = 33MHz)                |     |

| Table 3-11: AC Timing Characteristics - PCI Bus Stop (CLK = 33MHz)                 |     |

| Table 3-12: AC Timing Characteristics - BIOS ROM                                   |     |

| Table 3-13: AC Timing Characteristics - Video Data Port                            |     |

| Table 3-14: AC Timing Characteristics - Panel Output Timing                        |     |

| Table 3-15: AC Timing Characteristics - A.G.P. 1x AC Timing Parameters             |     |

| Table 6-1: PCI Configuration Registers                                             |     |

| Table 6-2: General Control & Status Registers                                      |     |

| Table 6-3: CRT Controller Registers                                                |     |

| Table 6-4: Sequencer Registers                                                     |     |

| Table 6-5: Graphics Controller Registers                                           |     |

| Table 6-6: Attribute Controller Registers                                          |     |

| Table 6-7: Palette Registers                                                       |     |

| Table 6-8: Extension Registers                                                     |     |

| Table 6-9: Flat Panel Registers                                                    |     |

| Table 6-10: Multimedia Registers                                                   |     |

| Table 6-11: BitBLT Registers                                                       |     |

| Table 6-12: Memory Mapped Wide Extension Registers                                 |     |

| Table 7-1: PCI Configuration Registers                                             |     |

| Table 15-1: Flat Panel Registers                                                   |     |

| Table 16-1: Multimedia Registers                                                   |     |

| Table 16-2: Color Key Bit Assignments                                              |     |

| Table A-1: Standard VGA CRT-Only Display Modes                                     |     |

| Table A-2: Extended VGA CRT-Only Display Modes                                     |     |

| Table A-3: Flat Panel-Only and Simultaneous 640x480 (VGA) Display Modes            |     |

| Table A-4: Flat Panel-Only and Simultaneous Display Modes for 800x600 Panels       |     |

| Table A-5: Flat Panel-Only and Simultaneous Display Modes for 1024x768 Flat Panels |     |

| Table A-6: Flat Panel-Only and Simultaneous Display Modes for 1280x1024 Flat Panel |     |

| Table D-1:         Memory Organization 32x32x2bpp AND/XOR Pixel Plane Mode         |     |

| Table D-2: Memory Organization 64x64x2bpp AND/XOR Pixel Plane Mode                 |     |

| Table D-3: Pixel Data 32x32x2bpp and 64x64x2bpp AND/XOR Pixel Plane Modes          |     |

| Table D-4:         Memory Organization 64x64x2bpp 4-Color Mode                     |     |

| Table D- 5: Pixel Data 64x64x2bpp 4-Color Mode                                     |     |

| Table D-6:         Memory Organization 64x64x2bpp 3-Color & Transparency Mode      |     |

| Table D-7: Pixel Data 64x64x2bpp 3-Color & Transparency Mode                       |     |

| Table D-8:         Memory Organization 128x128x1bpp 2-Color Mode                   |     |

| Table D-9: Pixel Data 128x128x1bpp 2-Color Mode                                    |     |

| Table D-10: Memory Organization 128x128x1bpp 1-Color & Transparency Mode           |     |

| Table D-11: Pixel Bit Definitions 128x128x1bpp 1-Color & Transparency Mode         |     |

| Table E-1: Bit-Wise Operations and 8-bit Codes (00 - 5F)                           |     |

| Table E-2: Bit-Wise Operations and 8-bit Codes (60 - BF)                           |     |

| Table E-3: Bit-Wise Operations and 8-bit Codes (C0 - FF)                           | E-6 |

# Chapter 1 Introduction / Overview

The 69000 is the first product in the CHIPS family of portable graphics accelerator product line that integrates high performance memory technology for the graphics frame buffer. Based on the proven HiQVideo<sup>™</sup> graphics accelerator core, the 69000 combines state-of-the-art flat panel controller capabilities with low power, high performance integrated memory. The result is the start of a high performance, low power, highly integrated solution for the premier family of portable graphics products.

# **High Performance Integrated Memory**

The 69000 is the first member of the HiQVideo<sup>™</sup> family to provide integrated high performance synchronous DRAM (SDRAM) memory technology. Targeted at the mainstream notebook market, the 69000 incorporates 2MB of proprietary integrated SDRAM for the graphics/video frame buffer. The integrated SDRAM memory can support up to 83MHz operation, thus increasing the available memory bandwidth for the graphics subsystem. The result is support for additional high color / high resolution graphics modes combined with real-time video acceleration. This additional bandwidth also allows more flexibility in the other graphics functions intensely used in Graphical User Interfaces (GUIs) such as Microsoft<sup>™</sup> Windows<sup>™</sup>.

## Frame-Based AGP Compatibility

The 69000 graphics is designed to be used with either 33MHz PCI, or with AGP as a frame-based AGP device, allowing it to be used with the AGP interface provided by the latest core logic chipsets.

# HiQColor<sup>TM</sup> Technology

The 69000 integrates CHIPS breakthrough HiQColor<sup>™</sup> technology. Based on the CHIPS proprietary TMED<sup>™</sup> (Temporal Modulated Energy Distribution) algorithm, HiQColor technology is a unique process that allows the display of 16.7 million true colors on STN panels without using Frame Rate Control (FRC) or dithering. In addition, TMED also reduces the need for the panel tuning associated with current FRC-based algorithms. Independent of panel response, the TMED algorithm eliminates all of the flaws (such as shimmer, Mach banding, and other motion artifacts) normally associated with dithering and FRC. Combined with the new fast response, high-contrast, and low-crosstalk technology found in new STN panels, HiQColor technology enables the best display quality and color fidelity previously only available with TFT technology.

### **Versatile Panel Support**

The HiQVideo<sup>™</sup> family supports a wide variety of monochrome and color Single-Panel, Single-Drive (SS) and Dual-Panel, Dual Drive (DD), standard and high-resolution, passive STN and active matrix TFT/MIM LCD, and EL panels. With HiQColor<sup>™</sup> technology, up to 256 gray scales are supported on passive STN LCDs. Up to 16.7M different colors can be displayed on passive STN LCDs and up to 16.7M colors on 24-bit active matrix LCDs.

The 69000 offers a variety of programmable features to optimize display quality. Vertical centering and stretching are provided for handling modes with less than 480 lines on 480-line panels. Horizontal and vertical stretching capabilities are also available for both text and graphics modes for optimal display of VGA text and graphics modes on 800x600, 1024x768 and 1280x1024 panels.

# **Television NTSC/PAL Flicker Free Output**

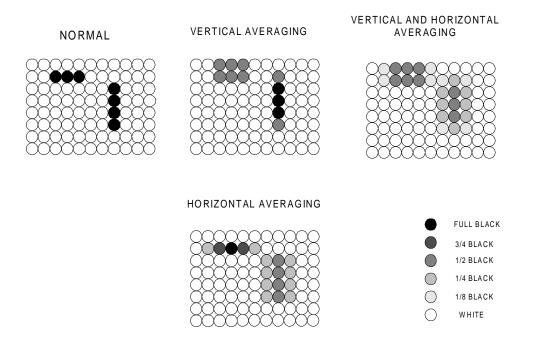

The 69000 uses a flicker reduction process which makes text of all fonts and sizes readable by reducing the flicker and jumping lines on the display. To accomplish this, the 69000 uses a line buffer and digital filters to average adjacent vertical lines for odd/even display. The chip also uses both horizontal and vertical interpolation to make both graphics and text appear "smooth" on the television. This process reduces the effect of flicker in the NTSC mode.

Flicker reduction can be accomplished by averaging the contents of successive horizontal and vertical lines. See Figure 1-1. The flicker reduction circuit is in pixel data path, with the vertical averaging circuit followed by the horizontal averaging circuit. Both have bypass controls (Vertical filter enable and Horizontal filter enable). This flicker averaging circuit is placed before the DAC and before the flat panel pick off. The flat panel pins can be used for test verification of correct filter operation.

Figure 1-1: Pixel Averaging Circuit

For the non-flicker reduction mode, the display line data is stored sequentially in the FIFO buffer. For the flicker reduction mode the FIFO buffer data is written in strips of *segments* because the vertical filter averages the current and next line pixels. Each segment is written to alternate locations in the FIFO buffer. See Fig. 1-2.

The write pointer is modified to skip through the FIFO buffer. A current/next line flag is carried through the display pipeline to keep track of which line the pixel comes from. This is needed for the color key logic and the vertical filter averaging circuitry to align to the correct segment of pixels. The MMUX color key is formed on the "current" pixel pair.

Flicker reduced NTSC is supported in the following extended graphics modes:

NTSC: 640x480, 60 Hz Interlaced PAL: 800x600, 50 Hz, Interlaced Color Depths: 8 bit indexed 15 bit RGB 16 bit RGB 24 bit RGB

# HiQVideo<sup>TM</sup> Multimedia Support

The 69000 uses independent multimedia capture and display systems on-chip. The capture system places data in display memory (usually off screen) and the display system places the data in a window on the screen.

The capture system can receive data from either the system bus or from the ZV enabled video port in either RGB or YUV format. The input data can also be scaled down before storage in display memory. Capture of input data may also be double buffered for smoothing and to prevent image tearing. To better support MPEG2 (DVD) video decompression, the 69000 includes a line buffer to directly support the native format of MPEG2 data of 720 pixels wide.

The capture engine also supports image mirroring and rotation for camera support. This feature is important for applications such as video teleconferencing because it allows the image movements to appear on the display as it actually occurs. The image and movement is not a mirror image of what is actually taking place. The display system can independently place either RGB or YUV data from anywhere in display memory into an on-screen window which can be any size and located at any pixel boundary (YUV data is converted to RGB "on-the-fly" on output). This is important for the 69000 since the video must be stored in the integrated 2MB frame buffer and thus optimized to require very little space. Storing data in the native YUV format uses less memory for video while providing excellent playback display quality.

Non-rectangular windows are supported via color keying. The data can be fractionally zoomed on output up to 8x to fit the on-screen window and can be horizontally and vertically interpolated. Interlaced and non-interlaced data are both supported in the capture and display systems.

# Low Power Consumption

The 69000 uses a variety of advanced power management features to reduce power consumption of the display sub-system and to extend battery life. Optimized for 3.3V operation, the 69000 internal logic, bus and panel interfaces operate at 3.3V but can tolerate 5V operation.

# Software Compatibility / Flexibility

The HiQVideo controllers are fully compatible with the VGA standard at both the register and BIOS levels. CHIPS and third-party vendors supply a fully VGA compatible BIOS, end-user utilities and drivers for common application programs.

# Acceleration for All Panels and All Modes

The 69000 graphics engine is designed to support high performance graphics and video acceleration for all supported display resolutions, display types, and color modes. There is no compromise in performance operating in 8, 16, or 24 bpp color modes allowing true acceleration while displaying up to 16.7M colors.

# **Display Modes Supported**

The 69000 supports the modes which appear in the table below.

| Table      | Table 1-1: 69000 Mode Support |                    |  |  |  |  |  |  |  |  |  |  |

|------------|-------------------------------|--------------------|--|--|--|--|--|--|--|--|--|--|

| Resolution | Color (bpp)                   | Refresh Rates (Hz) |  |  |  |  |  |  |  |  |  |  |

| 640x480    | 8                             | 60, 75, 85         |  |  |  |  |  |  |  |  |  |  |

| 640x480    | 16                            | 60, 75, 85         |  |  |  |  |  |  |  |  |  |  |

| 640x480    | 24                            | 60, 75, 85         |  |  |  |  |  |  |  |  |  |  |

| 800x600    | 8                             | 60, 75, 85         |  |  |  |  |  |  |  |  |  |  |

| 800x600    | 16                            | 60, 75, 85         |  |  |  |  |  |  |  |  |  |  |

| 800x600    | 24                            | 60, 75, 85         |  |  |  |  |  |  |  |  |  |  |

| 1024x768   | 8                             | 60, 75, 85         |  |  |  |  |  |  |  |  |  |  |

| 1024x768   | 16                            | 60, 75, 85         |  |  |  |  |  |  |  |  |  |  |

| 1280x1024  | 8                             | 60                 |  |  |  |  |  |  |  |  |  |  |

###

# Chapter 2 Pin Descriptions

# Pin Diagram, Top View

|    | А      | В      | С      | D      | Е      | F     | G      | Н      | J    | Κ      | L      | М     | Ν      | Ρ      | R   | Т     | U          | V           | W      | Y      | _  |

|----|--------|--------|--------|--------|--------|-------|--------|--------|------|--------|--------|-------|--------|--------|-----|-------|------------|-------------|--------|--------|----|

| 20 | CFG4   | CFG2   | N/C    | N/C    | N/C    | N/C   | N/C    | N/C    | N/C  | N/C    | RMA17  | N/C   | N/C    | N/C    | N/C | N/C   | VP1        | VP6         | VP10   | RSVD   | 20 |

| 19 | CFG6   | CFG5   | CFG1   | N/C    | N/C    | N/C   | N/C    | N/C    | N/C  | N/C    | RMA16  | N/C   | N/C    | N/C    | N/C | VP2   | VP5        | VP9         | VP11   | VP14   | 19 |

| 18 | N/C    | CFG7   | CFG3   | CFG0   | N/C    | N/C   | N/C    | N/C    | N/C  | N/C    | N/C    | N/C   | N/C    | N/C    | VP0 | VP4   | VP8        | VP13        | VP15   | VCLK   | 18 |

| 17 | RMA2   | N/C    | CFG8   | TMD0   | N/C    | N/C   | MEMGND | MEMVCC | N/C  | N/C    | N/C    | N/C   | MEMVCC | MEMGND | VP3 | VP7   | VP12       | PCLK        | HREF   | P33    | 17 |

| 16 | RMA4   | RMA1   | N/C    | CFG9   |        |       |        |        |      |        |        |       |        |        |     |       | GPIO4      | VREF        | P34    | P31    | 16 |

| 15 | RMA7   | RMA5   | RMA3   | RMA0   |        |       |        |        |      |        |        |       |        |        |     |       | P35        | P32         | P30    | P28    | 15 |

| 14 | RMA10  | RMA8   | RMA6   | MEMGND |        |       |        |        |      |        |        |       |        |        |     |       | GND        | P29         | P27    | P25    | 14 |

| 13 | RMA14  | RMA11  | RMA9   | MEMVCC |        |       |        |        |      |        |        |       |        |        |     |       | IOVCC      | P26         | P24    | P21    | 13 |

| 12 | TMD1   | RMA15  | RMA13  | RMA12  |        |       |        | 12     | GND  | GND    | GND    | RGND  | Ι      |        |     |       | P23        | P22         | CORVCC | P20    | 12 |

| 11 | N/C    | N/C    | N/C    | N/C    |        |       |        | 11     | GND  | GND    | GND    | RGND  |        |        |     |       | P16        | P19         | P18    | P17    | 11 |

| 10 | N/C    | CFG10  | CFG11  | N/C    |        |       |        | 10     | GND  | GND    | GND    | RGND  |        |        |     |       | P15        | P12         | P13    | P14    | 10 |

| 9  | CFG12  | CFG13  | CFG15  | CORVCC |        |       |        | 9      | GND  | GND    | GND    | RGND  |        |        |     |       | P7         | P8          | P10    | P11    | 9  |

| 8  | CFG14  | RMD0   | RMD2   | RSVD   |        |       |        |        | J    | К      | L      | М     | L      |        |     |       | IOVCC      | P4          | P6     | P9     | 8  |

| 7  | RMD1   | RMD3   | RMD5   | GND    |        |       |        |        |      |        |        |       |        |        |     |       | GND        | P1          | P3     | P5     | 7  |

| 6  | RMD4   | RMD6   | ROMOE# | GPI07  |        |       |        |        |      |        |        |       |        |        |     |       | ENABKL     | М           | P0     | P2     | 6  |

| 5  | RMD7   | RSVD   | RSVD   | DCKVCC |        |       |        |        |      |        |        |       |        |        |     |       | DACVCC     | ENAVDD      | FLM    | SHFCLK | 5  |

| 4  | INT#   | DCKGND | DCKVCC | RSVD   | STNDBY | AD30  | GND    | IOVCC  | AD20 | TRDY#  | DEVSEL | AD13  | IOVCC  | GND    | AD2 | GPI01 | DDC<br>CLK | GRN         | ENAVEE | LP     | 4  |

| 3  | DCKGND | мскусс | REFCLK | RSVD   | AD31   | AD27  | AD24   | AD23   | AD19 | C/BE2# | SERR#  | AD14  | AD10   | C/BE0# | AD5 | AD1   | HSYNC      | DDC<br>DATA | BLUE   | RED    | 3  |

| 2  | MCKGND | DCLKIN | RSVD   | BUSCLK | AD29   | AD25  | IDSEL  | AD21   | AD17 | FRAME# | PERR#  | C/BE1 | AD12   | AD9    | AD7 | AD3   | AD0        | VSYNC       | RSET   | DACGND | 2  |

| 1  | RSVD   | MCLKIN | RESET# | AD28   | AD26   | C/BE# | AD22   | AD18   | AD16 | IRDY#  | STOP#  | PAR   | AD15   | AD11   | AD8 | AD6   | AD4        | GPI00       | IOVCC  | RGND   | 1  |

| 1  | А      | В      | С      | D      | E      | F     | G      | Н      | J    | K      | L      | М     | N      | Р      | R   | Т     | U          | V           | W      | Y      | ,  |

Figure 2-1: Pin Diagram, Ball Grid Array

#### v \٨/ v ш D М NI

Pin Diagram, Bottom View

|    | Y      | W      | V           | U          | Т     | R   | Р      | Ν      | М     | L      | К      | J    | Н      | G      | F      | Е      | D      | С      | В      | А      | _  |

|----|--------|--------|-------------|------------|-------|-----|--------|--------|-------|--------|--------|------|--------|--------|--------|--------|--------|--------|--------|--------|----|

| 20 | RSVD   | VP10   | VP6         | VP1        | N/C   | N/C | N/C    | N/C    | N/C   | RMA17  | N/C    | N/C  | N/C    | N/C    | N/C    | N/C    | N/C    | N/C    | CFG2   | CFG4   | 20 |

| 19 | VP14   | VP11   | VP9         | VP5        | VP2   | N/C | N/C    | N/C    | N/C   | RMA16  | N/C    | N/C  | N/C    | N/C    | N/C    | N/C    | N/C    | CFG1   | CFG5   | CFG6   | 19 |

| 18 | VCLK   | VP15   | VP13        | VP8        | VP4   | VP0 | N/C    | N/C    | N/C   | N/C    | N/C    | N/C  | N/C    | N/C    | N/C    | N/C    | CFG0   | CFG3   | CFG7   | N/C    | 18 |

| 17 | P33    | HREF   | PCLK        | VP12       | VP7   | VP3 | MEMGND | MEMVCC | N/C   | N/C    | N/C    | N/C  | MEMVCC | MEMGND | N/C    | N/C    | TMD0   | CFG8   | N/C    | RMA2   | 17 |

| 16 | P31    | P34    | VREF        | GPIO4      |       |     |        |        |       |        |        |      |        |        |        |        | CFG9   | N/C    | RMA1   | RMA4   | 16 |

| 15 | P28    | P30    | P32         | P35        |       |     |        |        |       |        |        |      |        |        |        |        | RMA0   | RMA3   | RMA5   | RMA7   | 15 |

| 14 | P25    | P27    | P29         | GND        |       |     |        |        |       |        |        |      |        |        |        |        | MEMGND | RMA6   | RMA8   | RMA10  | 14 |

| 13 | P21    | P24    | P26         | IOVCC      |       |     |        |        |       |        |        |      |        |        |        |        | MEMVCC | RMA9   | RMA11  | RMA14  | 13 |

| 12 | P20    | CORVCC | P22         | P23        |       |     |        | 12     | RGND  | GND    | GND    | GND  | Ī      |        |        |        | RMA12  | RMA13  | RMA15  | TMD1   | 12 |

| 11 | P17    | P18    | P19         | P16        |       |     |        | 11     | RGND  | GND    | GND    | GND  | Ì      |        |        |        | N/C    | N/C    | N/C    | N/C    | 11 |

| 10 | P14    | P13    | P12         | P15        |       |     |        | 10     | RGND  | GND    | GND    | GND  | 1      |        |        |        | N/C    | CFG11  | CFG10  | N/C    | 10 |

| 9  | P11    | P10    | P8          | P7         |       |     |        | 9      | RGND  | GND    | GND    | GND  | 1      |        |        |        | CORVCC | CFG15  | CFG13  | CFG12  | 9  |

| 8  | P9     | P6     | P4          | IOVCC      |       |     |        | I      | М     | L      | К      | J    | -      |        |        |        | RSVD   | RMD2   | RMD0   | CFG14  | 8  |

| 7  | P5     | P3     | P1          | GND        |       |     |        |        |       |        |        |      |        |        |        |        | GND    | RMD5   | RMD3   | RMD1   | 7  |

| 6  | P2     | P0     | М           | ENABKL     |       |     |        |        |       |        |        |      |        |        |        |        | GPIO7  | ROMOE# | RMD6   | RMD4   | 6  |

| 5  | SHFCLK | FLM    | ENAVDD      | DACVCC     |       |     |        |        |       |        |        |      |        |        |        |        | DCKVCC | RSVD   | RSVD   | RMD7   | 5  |

| 4  | LP     | ENAVEE | GRN         | DDC<br>CLK | GPI01 | AD2 | GND    | IOVCC  | AD13  | DEVSEL | TRDY#  | AD20 | IOVCC  | GND    | AD30   | STNDBY | RSVD   | DCKVCC | DCKGND | INT#   | 4  |

| 3  | RED    | BLUE   | DDC<br>DATA | HSYNC      | AD1   | AD5 | C/BE0# | AD10   | AD14  | SERR#  | C/BE2# | AD19 | AD23   | AD24   | AD27   | AD31   | RSVD   | REFCLK | мскусс | DCKGND | 3  |

| 2  | DACGND | RSET   | VSYNC       | AD0        | AD3   | AD7 | AD9    | AD12   | C/BE1 | PERR#  | FRAME# | AD17 | AD21   | IDSEL  | AD25   | AD29   | BUSCLK | RSVD   | DCLKIN | MCKGND | 2  |

| 1  | RGND   | IOVCC  | GPI00       | AD4        | AD6   | AD8 | AD11   | AD15   | PAR   | STOP#  | IRDY#  | AD16 | AD18   | AD22   | C/BE3# | AD26   | AD28   | RESET# | MCLKIN | RSVD   | 1  |

|    | Y      | W      | V           | U          | Т     | R   | Р      | Ν      | М     | L      | Κ      | J    | Н      | G      | F      | E      | D      | С      | В      | А      |    |

Figure 2-2: Pin Diagram, Ball Grid Array

|   | 1          | 2              | 3             | 4          | 5           | 6             | 7              | 8             | 9              | 10         | 11         | 12         | 13         | 14         | 15         | 16    |   |

|---|------------|----------------|---------------|------------|-------------|---------------|----------------|---------------|----------------|------------|------------|------------|------------|------------|------------|-------|---|

| А | DCLKIN     | MCK<br>GND     | DCK<br>GND    | ROMOE#     | GPIO7       | RMD1<br>CFG14 | RMA15<br>CFG10 | RMA12         | RMA6           | RMA3       | CFG8       | CFG3       | CFG0       | TMD0       | N/C        | N/C   | А |

| В | RSVD       | N/C            | REF<br>CLK    | DCK<br>VCC | INT#        | RMD6          | RMD2<br>CFG15  | TMD1          | RMA14<br>CFG12 | RMA9       | RMA4       | CFG9       | CFG4       | N/C        | N/C        | N/C   | В |

| С | BUS<br>CLK | AD30           | STND<br>BY    | N/C        | DCK<br>GND  | RMD4          | COR<br>VCC     | N/C           | RMA10          | RMA5       | RMA0       | CFG5       | N/C        | N/C        | N/C        | N/C   | С |

| D | AD26       | AD24           | AD31          | MCK<br>VCC | N/C         | RMD7          | RMD3           | COR<br>VCC    | RMA11          | RMA7       | RMA1       | CFG6       | N/C        | MEM<br>GND | N/C        | N/C   | D |

| Е | IDSEL      | AD22           | AD27          | RESET#     | MCLKIN      | DCK<br>VCC    | RMD5           | RMD0<br>CFG13 | RMA13<br>CFG11 | RMA8       | RMA2       | CFG1       | N/C        | MEM<br>GND | N/C        | N/C   | Е |

| F | AD20       | AD18           | C/BE3#        | AD25       | AD29        | GND           | GND            | GND           | GND            | MEM<br>VCC | CFG7       | CFG2       | N/C        | MEM<br>GND | N/C        | N/C   | F |

| G | AD16       | C/BE2#         | AD19          | AD21       | AD28        | GND           | IOVCC          | IOVCC         | GND            | MEM<br>VCC | MEM<br>VCC | MEM<br>VCC | MEM<br>VCC | MEM<br>VCC | MEM<br>GND | N/C   | G |

| н | IRDY#      | TRDY#          | FRAME#        | AD17       | AD23        | GND           | IOVCC          | GND           | GND            | GND        | GND        | GND        | GND        | GND        | MEM<br>GND | N/C   | Н |

| J | STOP#      | PAR            | PERR#         | SERR#      | DEV<br>SEL# | C/BE1#        | COR<br>VCC     | IOVCC         | GND            | MEM<br>GND | GND        | GND        | GND        | GND        | MEM<br>GND | N/C   | J |

| К | AD15       | AD13           | AD12          | AD14       | AD10        | RED           | HSYNC          | IOVCC         | P15            | P21        | IOVCC      | IOVCC      | IOVCC      | GND        | MEM<br>VCC | N/C   | К |

| L | AD11       | AD9            | AD8           | AD7        | AD5         | IOVCC         | FLM            | P9            | MEM<br>VCC     | P22        | IOVCC      | IOVCC      | VP15       | VP7        | GND        | N/C   | L |

| М | C/BE0#     | AD6            | AD3           | AD1        | DAC<br>GND  | М             | P4             | P11           | P20            | P24        | P28        | P32        | HREF       | VP13       | VP6        | VP3   | М |

| Ν | AD4        | AD2            | GPIO0<br>ACTI | DDCK       | ENA<br>VDD  | P1            | P6             | P13           | IOVCC          | P26        | P33        | PCLK       | VP11       | VP4        | VP0        | N/C   | Ν |

| Ρ | AD0        | GPIO1<br>32KHZ | RGND          | GREEN      | LP          | P2            | P8             | COR<br>VCC    | P19            | P25        | P31        | P35        | GPIO4      | VP10       | VP5        | VP2   | Ρ |

| R | VSYNC      | DDC<br>DATA    | DAC<br>VCC    | ENA<br>BKL | P0          | P5            | P10            | P14           | P17            | P23        | P29        | P34        | VCLK       | VP12       | VP8        | RMA17 | R |

| т | RSET       | BLUE           | ENA<br>VEE    | SHF<br>CLK | Р3          | P7            | P12            | P16           | P18            | P27        | P30        | VREF       | VP14       | VP9        | VP1        | RMA16 | Т |

|   | 1          | 2              | 3             | 4          | 5           | 6             | 7              | 8             | 9              | 10         | 11         | 12         | 13         | 14         | 15         | 16    |   |

#### Pin Diagram, Top View

Figure 2-3: Pin Diagram, Mini Ball Grid Array

|   | 16    | 15         | 14         | 13         | 12         | 11         | 10         | 9              | 8             | 7              | 6             | 5           | 4          | 3             | 2              | 1          |   |

|---|-------|------------|------------|------------|------------|------------|------------|----------------|---------------|----------------|---------------|-------------|------------|---------------|----------------|------------|---|

| А | N/C   | N/C        | TMD0       | CFG0       | CFG3       | CFG8       | RMA3       | RMA6           | RMA12         | RMA15<br>CFG10 | RMD1<br>CFG14 | GPIO7       | ROMOE#     | DCK<br>GND    | MCK<br>GND     | DCLKIN     | А |

| В | N/C   | N/C        | N/C        | CFG4       | CFG9       | RMA4       | RMA9       | RMA14<br>CFG12 | TMD1          | RMD2<br>CFG15  | RMD6          | INT#        | DCK<br>VCC | REF<br>CLK    | N/C            | RSVD       | В |

| С | N/C   | N/C        | N/C        | N/C        | CFG5       | RMA0       | RMA5       | RMA10          | N/C           | COR<br>VCC     | RMD4          | DCK<br>GND  | N/C        | STND<br>BY    | AD30           | BUS<br>CLK | С |

| D | N/C   | N/C        | MEM<br>GND | N/C        | CFG6       | RMA1       | RMA7       | RMA11          | COR<br>VCC    | RMD3           | RMD7          | N/C         | MCK<br>VCC | AD31          | AD24           | AD26       | D |

| Е | N/C   | N/C        | MEM<br>GND | N/C        | CFG1       | RMA2       | RMA8       | RMA13<br>CFG11 | RMD0<br>CFG13 | RMD5           | DCK<br>VCC    | MCLKIN      | RESET#     | AD27          | AD22           | IDSEL      | Е |

| F | N/C   | N/C        | MEM<br>GND | N/C        | CFG2       | CFG7       | MEM<br>VCC | GND            | GND           | GND            | GND           | AD29        | AD25       | C/BE3#        | AD18           | AD20       | F |

| G | N/C   | MEM<br>GND | MEM<br>VCC | MEM<br>VCC | MEM<br>VCC | MEM<br>VCC | MEM<br>VCC | GND            | IOVCC         | IOVCC          | GND           | AD28        | AD21       | AD19          | C/BE2#         | AD16       | G |

| н | N/C   | MEM<br>GND | GND        | GND        | GND        | GND        | GND        | GND            | GND           | IOVCC          | GND           | AD23        | AD17       | FRAME#        | TRDY#          | IRDY#      | Н |

| J | N/C   | MEM<br>GND | GND        | GND        | GND        | GND        | MEM<br>GND | GND            | IOVCC         | COR<br>VCC     | C/BE1#        | DEV<br>SEL# | SERR#      | PERR#         | PAR            | STOP#      | J |

| к | N/C   | MEM<br>VCC | GND        | IOVCC      | IOVCC      | IOVCC      | P21        | P15            | IOVCC         | HSYNC          | RED           | AD10        | AD14       | AD12          | AD13           | AD15       | К |

| L | N/C   | GND        | VP7        | VP15       | IOVCC      | IOVCC      | P22        | MEM<br>VCC     | P9            | FLM            | IOVCC         | AD5         | AD7        | AD8           | AD9            | AD11       | L |

| М | VP3   | VP6        | VP13       | HREF       | P32        | P28        | P24        | P20            | P11           | P4             | м             | DAC<br>GND  | AD1        | AD3           | AD6            | C/BE0#     | М |

| Ν | N/C   | VP0        | VP4        | VP11       | PCLK       | P33        | P26        | IOVCC          | P13           | P6             | P1            | ENA<br>VDD  | DDCK       | GPIO0<br>ACTI | AD2            | AD4        | Ν |

| Ρ | VP2   | VP5        | VP10       | GPIO4      | P35        | P31        | P25        | P19            | COR<br>VCC    | P8             | P2            | LP          | GREEN      | RGND          | GPIO1<br>32KHZ | AD0        | Ρ |

| R | RMA17 | VP8        | VP12       | VCLK       | P34        | P29        | P23        | P17            | P14           | P10            | P5            | P0          | ENA<br>BKL | DAC<br>VCC    | DDC<br>DATA    | VSYNC      | R |

| т | RMA16 | VP1        | VP9        | VP14       | VREF       | P30        | P27        | P18            | P16           | P12            | P7            | P3          | SHF<br>CLK | ENA<br>VEE    | BLUE           | RSET       | Т |

|   | 16    | 15         | 14         | 13         | 12         | 11         | 10         | 9              | 8             | 7              | 6             | 5           | 4          | 3             | 2              | 1          |   |

#### Pin Diagram, Bottom View

Figure 2-4: Pin Diagram, Mini Ball Grid Array

| BGA I<br>PIN | mBGA<br>PIN | Pin Name | Туре | Active | Powered        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|-------------|----------|------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1           | E4          | RESET#   | In   | Low    | IOVCC<br>& GND | Reset. This input sets all signals and registers in<br>the chip to a known state. All outputs from the chip<br>are tri-stated or driven to an inactive state. This pin<br>is ignored during Standby mode (STNDBY# pin<br>low). The remainder of the system (therefore<br>the system bus) may be powered down if<br>desired (all bus output pins are tri-stated in<br>Standby mode).                                                                                                                                                                                                                             |

| D2           | C1          | BUSCLK   | In   | High   | IOVCC<br>& GND | Bus Clock. This input provides the timing reference<br>for all PCI and AGP bus transactions. All bus inputs<br>except RESET# are sampled on the rising edge of<br>BCLK. BCLK may be any frequency from DC up to<br>33MHz for PCI, or up to 66MHz for AGP.                                                                                                                                                                                                                                                                                                                                                       |

| M1           | J2          | PAR      | I/O  | High   | IOVCC<br>& GND | Parity. This signal is used to maintain even parity<br>across AD0-31 and C/BE0-3#. PAR is stable and<br>valid one clock after the address phase. For data<br>phases PAR is stable and valid one clock after<br>either IRDY# is asserted on a write transaction or<br>TRDY# is asserted on a read transaction. Once<br>PAR is valid, it remains valid until one clock after the<br>completion of the current data phase (i.e., PAR has<br>the same timing as AD0-31 but delayed by one<br>clock). The bus master drives PAR for address and<br>write data phases; the target drives PAR for read<br>data phases. |

| K2           | H3          | FRAME#   | In   | Low    | IOVCC<br>& GND | Cycle Frame. Driven by the current master to<br>indicate the beginning and duration of an access.<br>Assertion indicates a bus transaction is beginning<br>(while asserted, data transfers continue); de-<br>assertion indicates the transaction is in the final<br>data phase                                                                                                                                                                                                                                                                                                                                  |

| K1           | H1          | IRDY#    | In   | Low    | IOVCC<br>& GND | Initiator Ready. Indicates the bus master's ability to<br>complete the current data phase of the transaction.<br>During a write, IRDY# indicates valid data is present<br>on AD0-31; during a read it indicates the master is<br>prepared to accept data. A data phase is completed<br>on any clock when both IRDY# and TRDY# are<br>sampled then asserted (wait cycles are inserted<br>until this occurs).                                                                                                                                                                                                     |

| K4           | H2          | TRDY#    | S/TS | Low    | IOVCC<br>& GND | Target Ready. Indicates the target's ability to<br>complete the current data phase of the transaction.<br>During a read, TRDY# indicates that valid data is<br>present on AD0-31; during a write it indicates the<br>target is prepared to accept data. A data phase is<br>completed on any clock when both IRDY# and<br>TRDY# are sampled then asserted (wait cycles are<br>inserted until this occurs).                                                                                                                                                                                                       |

| L1           | J1          | STOP#    | S/TS | Low    | IOVCC<br>& GND | Stop. Indicates the current target is requesting the master to stop the current transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |